硅模具(PDMS芯片模具)是制备高深宽比PDMS芯片微通道的理想选择,利用硅的干法刻蚀技术,可以轻松实现深宽比最高达25:1的微通道结构,而且线条宽度可控制在2微米以上,精度误差仅在±1微米范围内。

然而,硅表面通常具有强烈的亲水性,这可能导致PDMS芯片在脱模时黏附在硅表面,制造过程中的一大挑战。

为解决这个问题,通常需要对硅表面进行疏水修饰,使硅表面变得疏水,确保PDMS芯片能够轻松从硅模具上脱离,而不受亲水性的干扰(具体疏水解决方案可咨询销售)。

硅的干法刻蚀

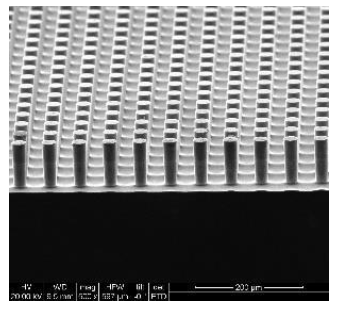

在制备PDMS芯片过程中,为了实现高深宽比的结构,通常采用的PDMS芯片模具是硅模具,硅模具是通过硅的干法刻蚀技术直接在硅表面加工出高深宽比的结构,在这一领域的领军者之一,德国斯图加特的Robert Bosch GmbH,提出了一项专利的DRIE方法,通过在高频电感耦合等离子体反应离子蚀刻(ICP-RIE)系统中交替执行蚀刻和沉积步骤,实现了高效而精密的微纳加工。

具体而言,该方法包括薄膜沉积、底部薄膜蚀刻和硅蚀刻三个关键步骤。在沉积工艺中,钝化膜被沉积在沟槽的侧壁和底面,而在底部膜蚀刻步骤中,通过选择性蚀刻沟槽底部上的钝化膜,实现了微结构的精细控制。最后,在硅蚀刻步骤中,仅蚀刻已去除钝化膜的沟槽底部的硅,进一步细化加工效果。

蚀刻过程中,垂直取向的离子(SFx+)起到了至关重要的作用,通过增强氟自由基,有效地去除了沟槽底部沉积的钝化膜,同时保持了薄膜沿侧壁的相对完整性。

蚀刻产生的侧壁纹理受到配方的影响,呈现出不同程度的扇形。值得注意的是,DRIE蚀刻速率随着沟槽深宽比的增加而降低,这为实现更加复杂的微结构提供了挑战。

硅表面疏水修饰

硅模具表面的强烈亲水性在PDMS芯片制备过程中可能引发黏附问题,成为制造中的一大挑战。为了解决这个问题,通常需要对硅模具表面进行疏水修饰,从而改变其表面性质,使其呈现出疏水性,减少与PDMS芯片的粘附。硅表面的疏水修饰是一个复杂而关键的步骤,涉及到多种表面处理技术。

一种常用的PDMS芯片模具疏水修饰方法是通过自组装单分子膜(Self-Assembled Monolayers,SAMs)的形成来实现。SAMs是由有机分子单层组成的自组装结构,可以在硅表面形成一个具有疏水性质的保护层。通常选择的有机分子包括长链烷烃或芳香族分子,它们的亲水尾部与硅表面结合,而亲水头部暴露在表面,改变了硅表面的化学性质。

另一种常见的PDMS芯片模具表面疏水修饰方法是化学气相沉积(Chemical Vapor Deposition,CVD)。通过CVD,可以在硅表面形成一层薄膜,通常是氢化非晶硅或四氢呋喃衍生物等材料,使硅表面发生化学改变,呈现出疏水性。这种方法具有高度可控性,可以实现对硅表面的精准疏水调控。

此外,等离子体辅助化学气相沉积(Plasma-Assisted Chemical Vapor Deposition,PACVD)也是一种有效的硅表面疏水修饰方法。

在等离子体的作用下,气相中的前体分子发生解离并沉积在硅表面,形成疏水性的薄膜。等离子体的存在使得沉积的薄膜更加致密和均匀,提高了修饰效果。

这些硅模具表面疏水修饰方法不仅可以防止PDMS芯片与硅表面的黏附,还可以提高芯片的耐久性和稳定性。

疏水修饰的硅表面在制备过程中有效减少了模具与芯片之间的粘附力,简化了脱模步骤,提高了制备效率。

通过选择合适的疏水修饰方法,可以根据实际需求对硅表面进行定制化处理,为PDMS芯片的制备提供了更灵活和可控的解决方案。

硅表面疏水修饰技术的发展不仅推动了微流控芯片制备工艺的进步,也在其他领域的材料科学和微纳加工中展现出广泛的应用前景。

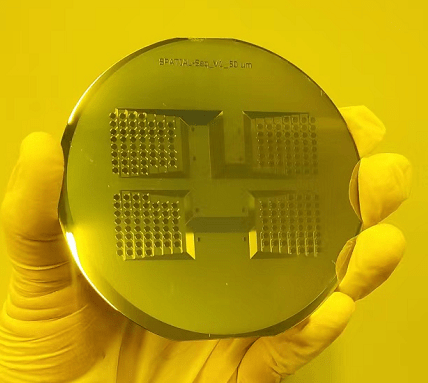

顶旭微控加工能力

◆加工工艺:深硅刻蚀

◆线条宽度:≥2um

◆深宽比:最大25:1

◆加工精度:±1um

◆表面处理:疏水处理

订购方式

© 2025. All Rights Reserved. 苏ICP备2022036544号-1