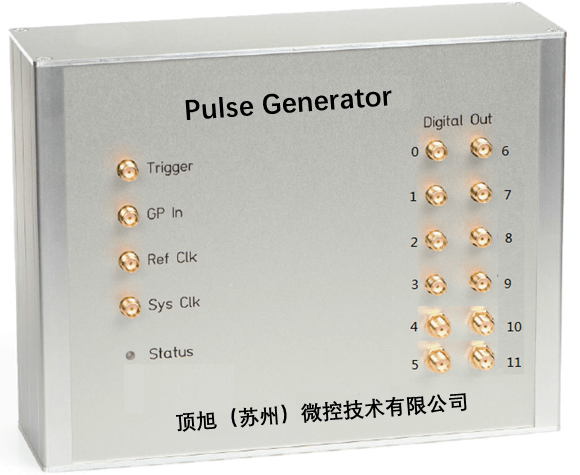

High-speed programmable pulse signal generator

The PulseBlasterESR-PRO™ is a high-speed intelligent pulse/pattern/delay generator designed to output precisely timed TTL patterns.The PulseBlasterESR-PRO derives its intelligence from an embedded microprogramming controller core nicknamed “PulseBlasterESR-PRO “.

Nicknamed PulseBlaster™, the embedded microprogram controller core. The controller is capable of executing instructions, allowing it to control program flow like a general-purpose microcontroller.The PulseBlasterESR-PRO derives its speed from a maximum available clock frequency of 500 MHz.

The PulseBlasterESR-PRO's microprogram controller core differs from a general-purpose microcontroller in that it contains a microprocessor core.

Unlike general-purpose microcontrollers, which contain a highly optimized set of instructions developed specifically for timing and control applications, the PulseBlasterESR-PRO processor is unique in that the execution time of the instructions can be programmed by the user. This feature allows the PulseBlasterESR-PRO processor to execute complex timing patterns at different update rates ranging from nanoseconds to months.

nanoseconds to months, while the setup accuracy is always maintained to one clock cycle.

Model parameters

| model number | parameters |

| PBESR-PRO-500-PCI | 500 MHz21 channelsPCI connector2.0 ns pulse resolution2.0 ns shortest pulse4k memory words |

| PBESR-PRO-500-PCIe | 500 MHz21 channelsPCIe connector2.0 ns pulse resolution2.0 ns shortest pulse4k memory words |

| PBESR-PRO-500-USB-RM-FP | 500 MHz21 channelsUSB2U rackmount front panel 2.0 ns pulse resolution2.0 ns shortest pulse4k memory words |

| PBESR-PRO-500-USB-RM | 500 MHz21 channelsUSB2U rackmount/desktop enclosure2.0 ns pulse resolution2.0 ns shortest pulse4k memory words |

Key Specifications:

- Standard clock frequencies: up to 500 MHz for the PBESR-PRO series

- Up to 24 independently controlled output channels

- Up to 25 mA output current per channel

- Programmable pulse length from five clock cycles (50ns, 100MHz) to 7 days per command. Pulses can be as short as 2.0ns (500MHz, PulseBlasterESR-PRO series).

- 2ns pulse resolution

- 4K and 64K available pulse program instruction word storage depths

- Advanced pulse program flow control: nested loops (8 levels), branches and subroutines

- 20-bit cycle counter

- Software and hardware triggering, up to 5 MHz trigger frequency

- PCI, PCIe or Compact-PCI interface

Applications

- Electron, Nuclear and Quadrupole Resonance Testing and Process Control (ESR, NMR, NQR)

- Mass spectrometry and related detection techniques

- Ultrasound, Radar, Medical Imaging

- Communication laser control

- Solid State Physics Experiment

- Applications of nanomagnetism and spintronics

- Robot synchronization with processes

- Data bus simulation

- Laboratory use

products

Parameter

TTL Specifications

12 individually controlled digital output lines (LVTTL levels, 3.3 V logical “one” unterminated)

Variable pulses/delays for every TTL line

25 mA output current per TTL line

Pulse Parameters (using 500 MHz clock frequency)

2 ns shortest pulse

10 ns shortest interval1

2 ns pulse/interval resolution

64k instructions

External triggering and reset – 3.3V LVTTL levels

Pulse Program Control Flow (Common)

Loops, nested 8 levels deep

20 bit loop counters (max. 1,048,576 repetitions)

Subroutines, nested 8 levels deep

Wait for trigger – 8 clock cycle latency (16ns at 500 MHz), adjustable to 0.89 seconds in duration

15 MHz max. re-triggering frequenc

Site Search

© 2025. All Rights Reserved. 苏ICP备2022036544号-1